# Triple/Quadruple Patterning Layout Decomposition via Novel Linear Programming and Iterative Rounding

Yibo Lin<sup>1</sup>, Xiaoqing Xu<sup>1</sup>, Bei Yu<sup>2</sup>, Ross Baldick<sup>1</sup>, David Z. Pan<sup>1</sup>

<sup>1</sup>ECE Department, University of Texas at Austin <sup>2</sup>CSE Department, Chinese University of Hong Kong

This work is supported in part by NSF and SRC

#### Outline

•

- Introduction

- A New Framework for Layout Decomposition

- ILP  $\rightarrow$  LP relaxation with iterative rounding

- Experimental Results

- Conclusion

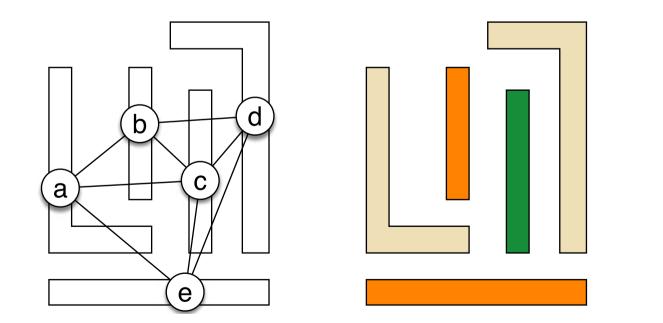

# **Triple Patterning Lithography (TPL)**

- An example of TPL conflict graph and decomposition

- Layout decomposition is a fundamental problem for multiple patterning

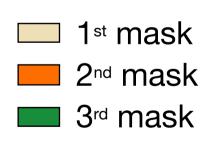

# **Quadruple Patterning Lithography (QPL)**

An example of QPL layout decomposition (coloring) and conflict graph

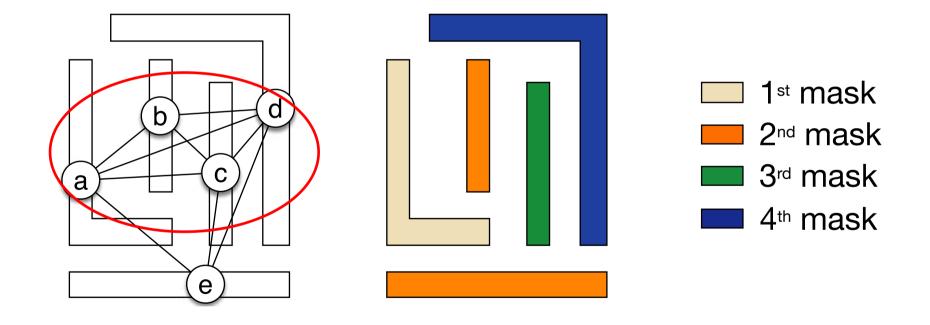

## **Stitch Insertion**

Stitch may be inserted to resolve conflict

- However, strongly discouraged due to misalignment and yield loss

- In this work, we do not allow stitch insertion

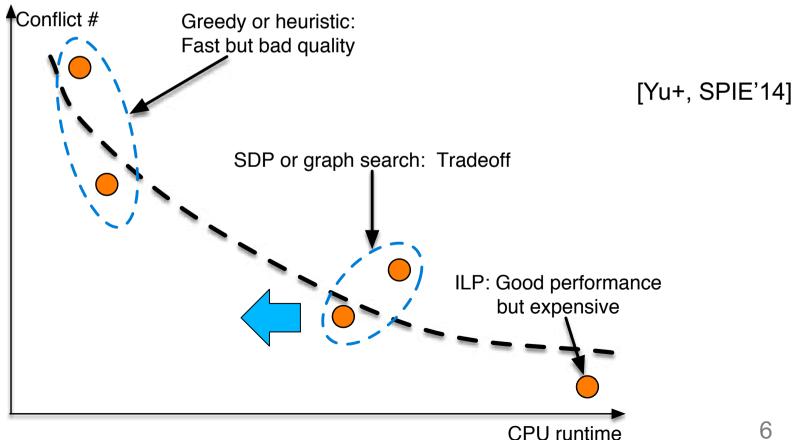

#### **Current State of MPL Decomposition**

- **ILP or SAT:** [Cork+, SPIE'08], [Yu+, ICCAD'11], [Cork+, SPIE'13]

- Greedy or heuristic: [Ghaida+, SPIE'11], [Fang+, DAC'12], [Kuang+, DAC'13], [Fang+, SPIE'14]

- SDP or graph search: [Yu+, ICCAD'11], [Chen+, ISQED'13], [Yu+, ICCAD'13], [Yu+, DAC'14]

#### **Major Contributions of This Work**

- A new layout decomposition framework for TPL/QPL

- ILP → novel linear programming (LP) based algorithm with iterative rounding scheme

- An odd-cycle based technique to enhance LP solution quality (which can be better mapped to ILP solution)

- Our experiments obtain comparable quality cf. previous state-of-the-art, but are 26x to 600x faster than ILP, and 1.8x to 2.6x faster than SDP

# **Problem Formulation**

- Input

- Uncolored layout patterns

- Minimum coloring distance  $d_c$

- Number of colors available (TPL or QPL)

- Output

- Decomposed layout with color assignment for each pattern

- TPL/QPL friendliness

- Stitch insertion is not allowed

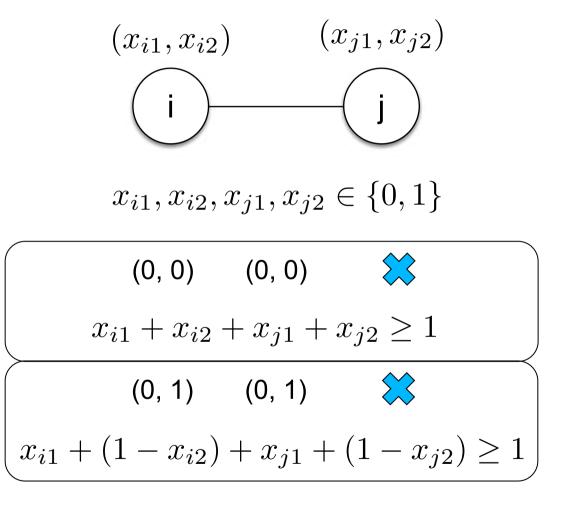

#### **Initial ILP Formulation**

Represent color with two binary variables

$(x_{i1}, x_{i2}) \rightarrow \text{color}$  $(0, 0) \rightarrow 0$  $(0, 1) \rightarrow 1$  $(1, 0) \rightarrow 2$  $(1, 1) \rightarrow 3$

Additional constraint for TPL

$x_{i1} + x_{i2} \le 1$

#### **ILP Formulation**

• The goal is to meet all the constraints

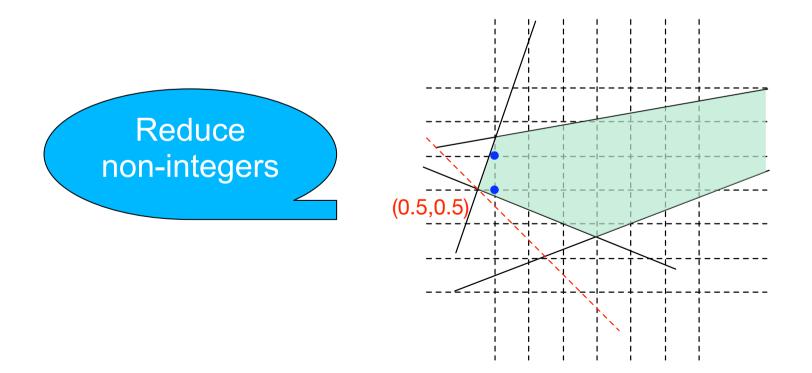

#### **LP Relaxation**

Relax integer to continuous variables

# LPIR

- Linear programming and iterative rounding (LPIR)

- Non-integer solutions

- Fewer non-integers mean closer to optimal solutions of ILP

- Prune non-integer solutions in the feasible set

#### **Simple Observation**

• Suppose

$$x_{i1} = x_{j1} = 0$$

$$(x_{i1}, x_{i2}) \qquad (x_{j1}, x_{j2})$$

$$\begin{array}{ll}

x_{i1} + x_{i2} + x_{j1} + x_{j2} \ge 1, & \forall e_{ij} \in E_c, \\

x_{i1} + \bar{x}_{i2} + x_{j1} + \bar{x}_{j2} \ge 1, & \forall e_{ij} \in E_c, \\

\bar{x}_{i1} + x_{i2} + \bar{x}_{j1} + x_{j2} \ge 1, & \forall e_{ij} \in E_c, \\

\bar{x}_{i1} + \bar{x}_{i2} + \bar{x}_{j1} + \bar{x}_{j2} \ge 1, & \forall e_{ij} \in E_c, \\

\hline x_{i1} + \bar{x}_{i2} + \bar{x}_{j1} + \bar{x}_{j2} \ge 1, & \forall e_{ij} \in E_c, \\

\end{array} \tag{1c}$$

$$\bar{x}_{i1} = 1 - x_{i1}, \quad \forall i \in V, \tag{1g}$$

$$\bar{x}_{i2} = 1 - x_{i2}, \quad \forall i \in V \tag{1h}$$

$$x_{i2} + x_{j2} = 1$$

The second bits must be different

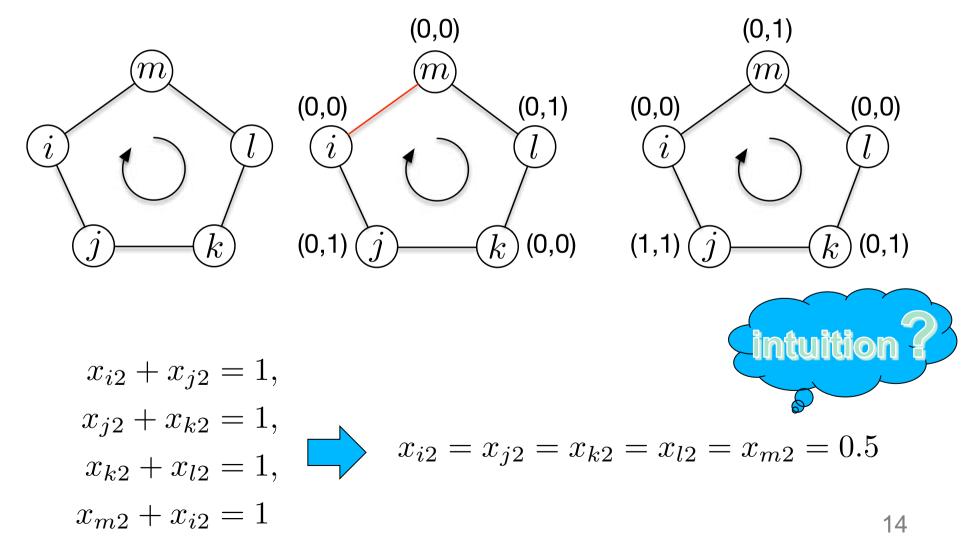

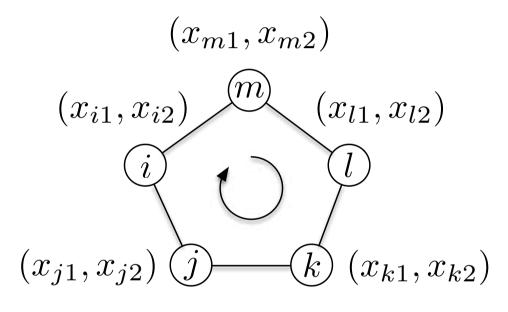

#### **Non-integers along Odd Cycles**

- Consider the constraints along an odd cycle

- Suppose  $x_{i1} = x_{j1} = x_{k1} = x_{l1} = x_{m1} = 0$

#### **LPIR – Add Odd Cycle Constraints**

- Additional constraints

- Prune non-integer solutions from feasible set

s.t.

$$x_{i1} + x_{j1} + x_{k1} + x_{l1} + x_{m1} \ge 1,$$

(1 - x<sub>i1</sub>) + (1 - x<sub>j1</sub>) + (1 - x<sub>k1</sub>) + (1 - x<sub>l1</sub>) + (1 - x<sub>m1</sub>) \ge 1

Help resolve potential non-integers in the second bits

#### **LPIR – Objective Function Biasing**

- Push non-integer solutions to integers by dynamically adapting the objective function

- If  $x_i = 0.6$ , it means  $x_i$  tends to be 1

- If  $x_i = 0.4$ , it means  $x_i$  tends to be 0

If

$$x_i > 0.5$$

,  $obj \leftarrow obj + (1 - x_i)$ .

If  $x_i < 0.5$ ,  $obj \leftarrow obj + x_i$ .

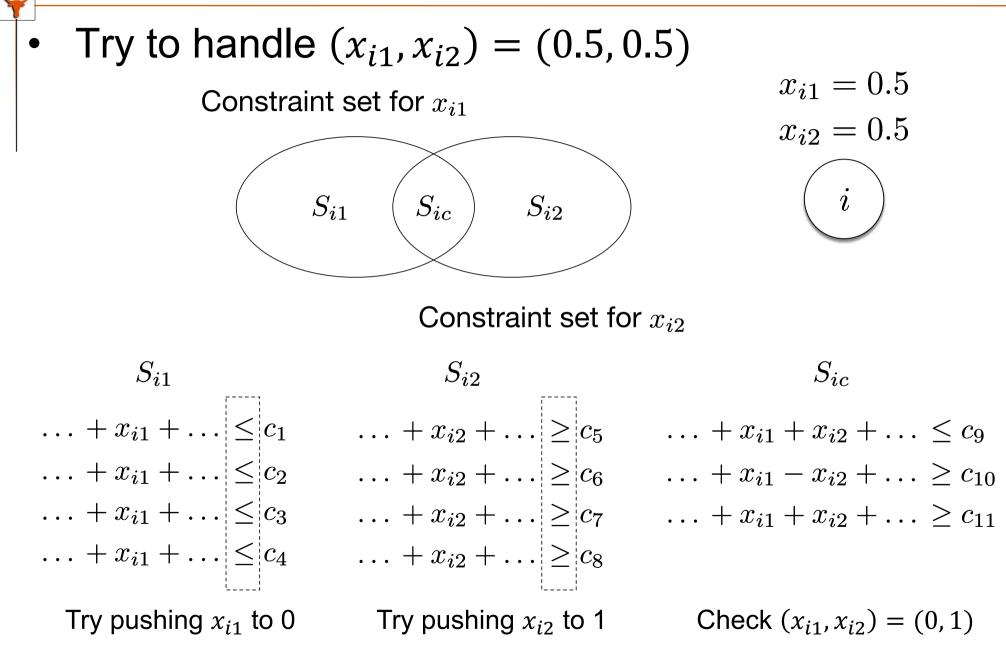

Cannot handle (0.5, 0.5)

#### **LPIR – Binding Constraints Analysis**

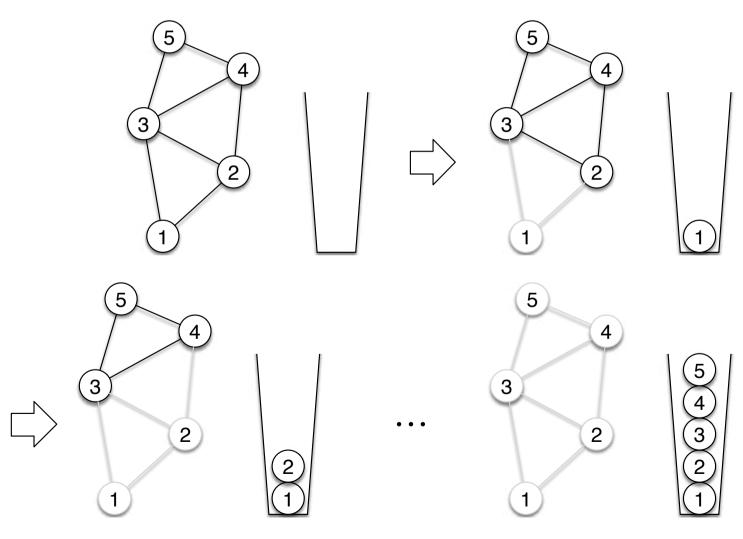

#### **Graph Simplification – Iterative Vertex Removal**

- Iterative vertex removal

- Density aware recovery

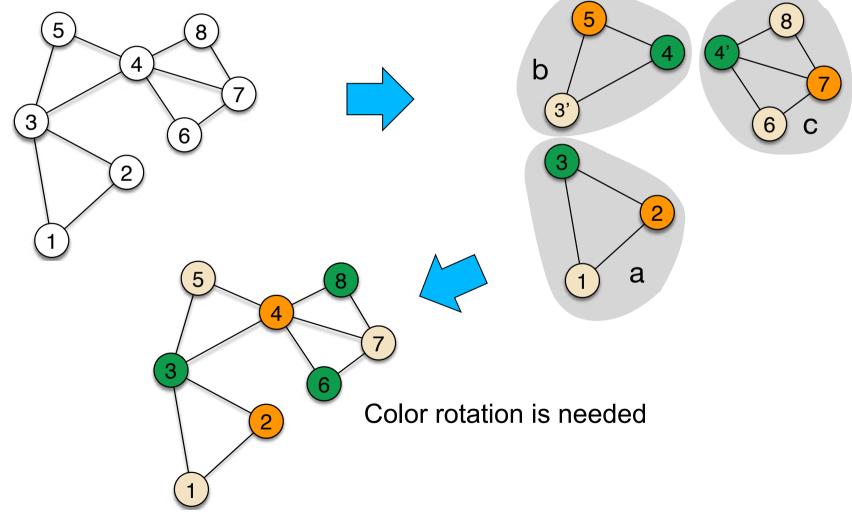

# **Graph Simplification: Bi-connected Component Extraction**

- Color recovery

- Color rotation on each component

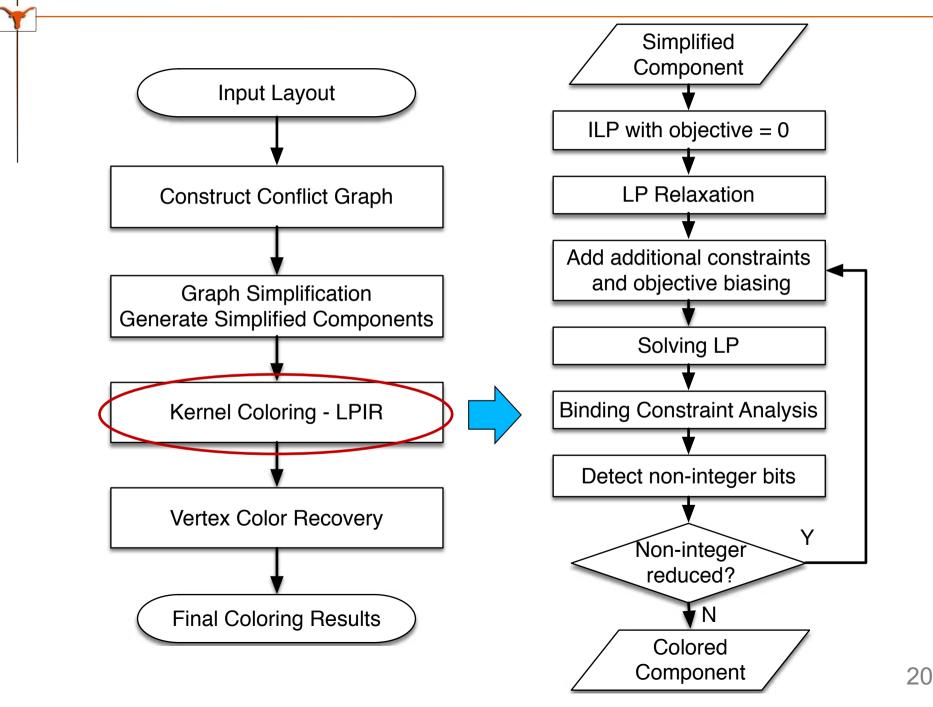

#### **Overall Flow**

#### **Experimental Environment Setup**

- Implemented in C++

- 8-Core 3.4GHz Linux server

- 32GB RAM

- ISCAS benchmark from [Yu+, TCAD'15]

- LP solver Gurobi was used

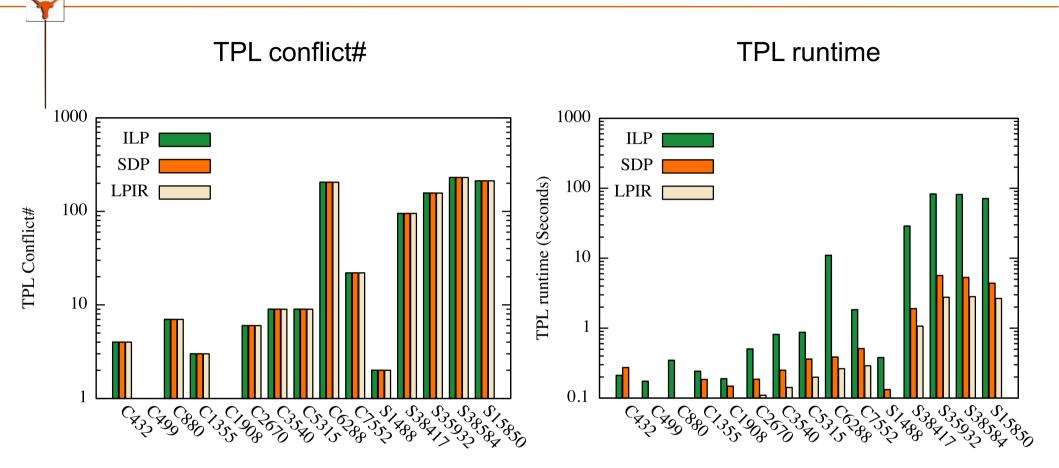

#### **Experimental Results on TPL**

Baseline 1: ILP [Yu+, TCAD'15] Baseline 2: SDP [Yu+, TCAD'15] LPIR achieves almost the same conflict numbers as ILP and SDP, but 26x faster than ILP and 1.8x faster than SDP

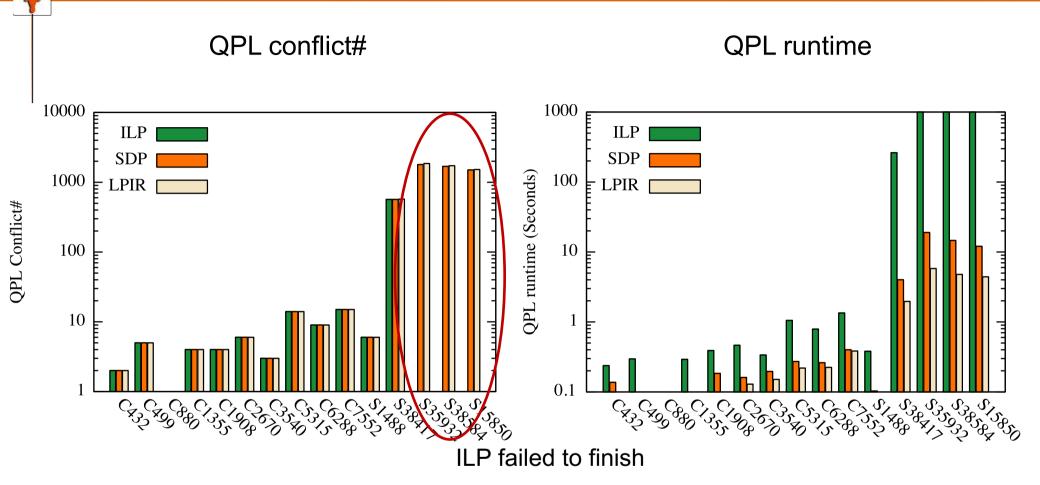

#### **Experimental Results on QPL**

Baseline 1: ILP [Yu+, DAC'14] Baseline 2: SDP [Yu+, DAC'14] LPIR achieves less than 2% degradation in conflict numbers than SDP, but 600x faster than ILP and 2.6x faster than SDP

#### Conclusion

- This paper proposes a new layout decomposition framework for TPL/QPL

- Novel linear programming (LP) based algorithm with iterative rounding

- Odd-cycle based pruning technique to enhance LP quality

- Very good results cf. previous state-of-the-art decomposer

- Future work

- Lithography impacts (e.g., hotspots) from different decomposition solutions

- Decomposition friendliness from early design stages like placement and routing

# Thanks!